# Hardware- and Software-Based Collective Communication on the Quadrics Network \*

Fabrizio Petrini, Salvador Coll, Eitan Frachtenberg and Adolfy Hoisie

CCS-3 Modeling, Algorithms, & Informatics Computer & Computational Sciences Division Los Alamos National Laboratory {fabrizio,scoll,eitanf,hoisie}@lanl.gov

## **Abstract**

The efficient implementation of collective communication patterns in a parallel machine is a challenging design effort, that requires the solution of many problems. In this paper we present an in-depth description of how the Quadrics network supports both hardware- and software-based collectives. We describe the main features of the two building blocks of this network, a network interface that can perform zero-copy user-level communication and a wormhole routing switch. We also focus our attention on the routing and flow control algorithms, deadlock avoidance and on how the processing nodes are integrated in a global, virtual shared memory.

Experimental results conducted on 64-node AlphaServer cluster indicate that the time to complete the hardware-based barrier synchronization on the whole network is as low as 6 µs, with very good scalability. Good latency and scalability are also achieved with the software-based synchronization, which takes about 15 µs. With the broadcast, similar performance is achieved by the hardware- and software-based implementations, which can deliver messages of up to 256 bytes in 13 µs and can get a sustained asymptotic bandwidth of 288 Mbytes/sec on all the nodes.

The hardware-based barrier is almost insensitive to the network congestion, with 93% of the synchronizations taking less than 20 µs when the network is flooded with a background traffic of unicast messages. On the other hand, the software-based implementation suffers from a significant performance degradation. With high load the hardware broadcast maintains a reasonably good latency, delivering messages up to 2KB in 200 µs, while the software broadcast suffers from slightly higher latencies inherited from the synchronization mechanism. Both broadcast algorithms experience a significative performance degradation of the sustained bandwidth with large messages.

# 1 Introduction

Many scientific applications exhibit the need of communication patterns which involve global data movement and global control [5]. Barrier synchronization, broadcast, gather, scatter, reduce and total exchange are typical examples of collective communication patterns.

Hardware or software support for multicast communication can substantially improve the performance and the resource utilization of a parallel computer. Software overhead accounts for a high percentage of the communication latency, and replacing several point-to-point primitives with a single multicast operation may substantially decrease the communication latency. Furthermore, when a node sends the same message towards several destinations, some of these replicated messages may traverse the same communication channels, generating more traffic than needed.

A common network design trend is to place a communication processor in the network interface [2]. This processor can quickly handle incoming messages and perform simple computations without interacting with the host node [3]. The close integration of these network processors with the capability of performing multicast communication is likely to play an important role in the near future. In fact, the multicast can be enhanced to perform some type of activemessage [16] computation on the set of destinations. This creates the opportunity of executing system-level operations to enhance fault-tolerance, for example to check the status of the processing nodes, perform distributed algorithms to balance the load, or to synchronize the local clocks. More generally, these mechanisms can help to integrate the resources in a parallel machine, as if they were a single seamless system.

Hardware support for multicast communication requires many functionalities, that are dependent on the network topology, the routing algorithm and the flow control strategy. For example, in a wormhole network, switches must be capable of forwarding flits from one input channel to multiple output channels at the same time in a tree-like fashion

<sup>\*</sup>The work was supported by the U.S. Department of Energy through Los Alamos National Laboratory contract W-7405-ENG-36

[14]. Unfortunately, these tree-based algorithms can suffer from blocking problems in the presence of congestion [15]. Also, the packets must be able to encode the set of destinations in an easy-to-decode, compact manner, in order to reduce the packet size and to guarantee fast routing times in the switches.

Software multicasts, based on unicast messages, are simpler to implement, do not require dedicated hardware and are not constrained by the network topology and routing algorithms, but they can be much slower than the hardware ones.

In this paper we analyze in depth how hardware- and software-based multicasts are designed and implemented in the Quadrics network (QsNET).

The paper is logically divided into two parts. In the first part we analyze the relevant design issues of the network. The list includes the main characteristics of the network interface, the communication libraries, how local memories are integrated in a global shared memory, the topology of the interconnection network, the routing algorithm, and the link-level and end-to-end flow control algorithms. This initial part introduces the mechanisms at the base of the hardware and software multicast primitives that, on their turn are at the base of more sophisticated collective communication patterns as broadcasts, barriers, scatter, gather, reduce, etc.

In the second part we provide an extensive performance evaluation of two user-level collective communication patterns, barrier and broadcast, implemented using both hardware and software multicast algorithms. One important contribution of this paper is the performance evaluation of these algorithms under network congestion.

The rest of this paper is organized as follows. Section 2 provides an overview of the QsNET hardware building blocks and their collective communication capabilities. Section 3 discusses the hierarchy of communication libraries, while Section 4 gives a detailed description of the main collective communication services. The experimental methodology is described in Section 5 and Section 6 presents the experimental results and performance analysis. Finally, in Section 7, some conclusions are drawn.

# 2 The QsNET

The QsNET is based on two building blocks, a programmable network interface called Elan [12] and a low-latency high-bandwidth communication switch called Elite [13]. Elites can be interconnected in a fat-tree topology [7]. The network has several layers of communication libraries which provide trade-offs between performance and ease of use. Other important features are hardware support for collective communication patterns and fault-tolerance.

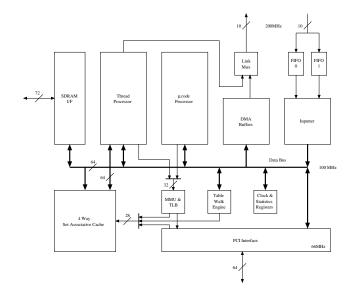

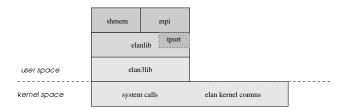

Figure 1. Elan Functional Units

## **2.1** Elan

The Elan<sup>1</sup> network interface links the high-performance, multi-stage Quadrics network to a processing node containing one or more CPUs. In addition to generating and accepting packets to and from the network, the Elan also provides substantial local processing power to implement high-level message-passing protocols such as MPI. The internal functional structure of the Elan, shown in Figure 1, centers around two primary processing engines: the microcode processor and the thread processor.

The 32-bit microcode processor supports four separate threads of execution, where each thread can independently issue pipelined memory requests to the memory system. Up to eight requests can be outstanding at any given time. The scheduling for the microcode processor is extraordinarily lightweight, enabling a thread to wake up, schedule a new memory access on the result of a previous memory access, and go back to sleep in as few as two system-clock cycles.

The four microcode threads are described below: (1) *in-putter thread:* Handles input transactions from the network. (2) *DMA thread:* Generates DMA packets to be written to the network, prioritizes outstanding DMAs, and time-slices large DMAs so that small DMAs are not adversely blocked. (3) *processor-scheduling thread:* Prioritizes and controls the scheduling and descheduling of the thread processor. (4) *command-processor thread:* Handles operations requested by the host processor at user level.

The thread processor is a 32-bit RISC processor used to aid the implementation of higher-level messaging libraries without explicit intervention from the main CPU. In order to better support this implementation, the thread processor's instruction set was augmented with extra instructions that

<sup>&</sup>lt;sup>1</sup>This paper refers to the Elan3 version of the Elan. We will use Elan and Elan3 interchangeably throughout the paper.

construct network packets, manipulate events, efficiently schedule threads, and block save and restore a thread's state when scheduling.

#### 2.2 Elite

The other building block of the QsNET is the Elite switch. The Elite provides the following features: (1) 8 bidirectional links supporting two virtual channels in each direction, (2) an internal  $16 \times 8$  full crossbar switch<sup>2</sup>, (3) a nominal transmission bandwidth of 400 MB/s on each link direction and a flow through latency of 35 ns, (4) packet error detection and recovery, with routing and data transactions CRC protected, (5) two priority levels combined with an aging mechanism to ensure a fair delivery of packets in the same priority level, (6) hardware support for broadcasts, (7) and adaptive routing.

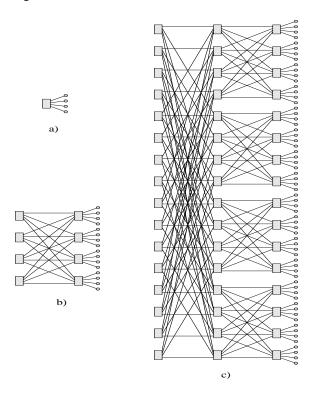

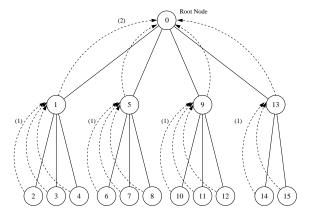

The Elite switches are interconnected in a quaternary fattree topology, which belongs to the more general class of the k-ary n-trees [9] [8]. A quaternary fat-tree of dimension n is composed of  $4^n$  processing nodes and  $n*4^{n-1}$  switches interconnected as a delta network, and can be recursively build by connecting 4 quaternary fat trees of dimension n-1.

Quaternary fat trees of dimension 1, 2 and 3 are shown in Figure 2.

Figure 2. 4-ary *n*-trees of dimension 1, 2 and 3

#### 2.2.1 Packet Routing and Flow Control

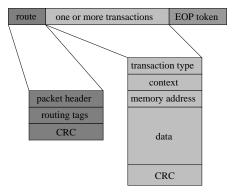

Each user- and system-level message is chunked in a sequence of packets by the Elan. An Elan packet contains three main components. The packet starts with the (1) routing information, that determines how the packet will reach the destination. This information is followed by (2) one or more transactions consisting of some header information, a remote memory address, the context identifier and a chunk of data, which can be up to 64 bytes in the current implementation. The packet is terminated by (3) an end of packet (EOP) token, as shown in Figure 3.

Figure 3. Packet Transaction Format

Transactions fall into two categories: write block transactions and non-write block transactions.

The purpose of a write block transaction is to write a block of data from the source node to the destination node, using the destination address contained in the transaction immediately before the data. A DMA operation is implemented as a sequence of write block transactions, partitioned into one or more packets (a packet normally contains 5 write block transactions of 64 bytes each, for a total of 320 bytes of data payload).

The non-write block transactions implement a family of relatively low level communication and synchronization primitives. For example, non-write block transactions can atomically perform remote test-and-write or fetch-and-add and return the result of the remote operation to the source, and can be used as building blocks for more sophisticated distributed algorithms.

Elite networks are source routed. The routing information is attached to the header before injecting the packet into the network and is composed of a sequence of Elite link tags. As the packet moves inside the network, each Elite removes the first routing tag from the header, and forwards the packet to the next Elite in the route or to the final destination. The routing tag can identify either a single output link or a group of adjacent links.

The transmission of each packet is pipelined into the network using wormhole switching. At link level, each packet is partitioned in smaller units called flits (flow control digits) [4] of 16 bits. The header flit opens a circuit between

<sup>&</sup>lt;sup>2</sup>The crossbar has two input ports for each input link, to accommodate the two virtual channels.

source and destination, and this path stays in place until the destination sends an acknowledgement to the source. At this point, the circuit is closed by sending an EOP token. It is worth noting that both acknowledgment and EOP can be tagged to communicate control information. So, for example, the destination can notify the successful completion of a remote non-write block transaction without explicitly sending an extra packet.

Minimal routing between any pair of nodes can be accomplished by sending the message to one of the nearest common ancestors and from there to the destination. That is, each packet experiences two routing phases, an adaptive ascending phase to get to a nearest common ancestor, followed by a deterministic descending phase. The Elite switches can adaptively route a packet picking the least loaded link.

#### 2.3 Collective Communication

Packets can be sent to multiple destinations using either the *hardware* multicast capability of the network or a *soft-ware* tree implemented with point-to-point communication between the Elan thread processors.

#### 2.3.1 Hardware Multicast

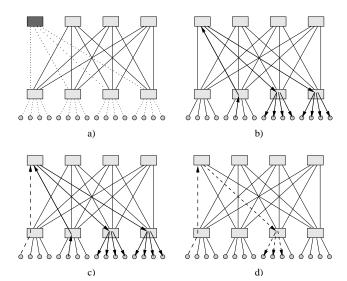

A multicast packet can only take a pre-determined path, in order to avoid deadlocks. In Figure 4 a) it is shown that the top leftmost switch is chosen as the logical root for the collective communication, and every request, in the ascending phase, must pass through one of the dotted paths until it gets to the root switch. In Figure 4 b) we can see how a multicast packet reaches the root node; the multiple branches are then propagated in parallel. If another collective communication is issued while the first one is still in progress, it is serialized in the root switch. The second multicast packet will be able to proceed only after an EOP token cleans the circuit of the first communication. All nodes connected to the network are capable of receiving the multicast packet, as long as the multicast set is physically contiguous.

For a multicast packet to be successfully delivered, a positive acknowledgement must be received from all the recipients of the multicast group. The Elite switches combine the acknowledgements, as pioneered by the NYU Ultracomputer [1] [10], returning a single one to the source. Acknowledgements are combined in a way that the "worst" ack wins (a network error wins over an unsuccessful transaction, which on its turn wins over a successful one), returning a positive ack only when all the partners in the collective communication complete the distributed transaction with success.

## 2.3.2 Software Tree

The Elan thread processor can receive an incoming packet, do some basic processing (such as an atomic increment of

Figure 4. Hardware Multicast

a variable) and send one or more replies in few  $\mu$ s, without any interaction with the main processors. Software collectives can be implemented using the communication and computation capability of the Elan thread processor, for example multicast trees. Software collectives can be based on trees with programmable arity, depth and regularity, and do not suffer from the limitation that the destination set must be composed of adjacent nodes.

#### 3 Programming libraries

The Elan network interface can be programmed using several programming libraries [11], as outlined in Figure 5. These libraries trade speed with machine independence and programmability. Starting from the bottom, Elan3lib is the lowest programming level available in user space which allows access to the low level features of the Elan3. At this level, processes in a parallel job can communicate with each other through an abstraction of distributed virtual shared memory. Each process in a parallel job is allocated a virtual process id (VPID) and can map a portion of its address space into the Elan. These address spaces, taken in combination, constitute a distributed virtual shared memory. Remote memory (i.e., memory on another node) can be addressed by a combination of a VPID and a virtual address. Since the Elan has its own MMU, a process can select which part of its address space should be visible across the network, determine specific access rights (e.g. writeor read-only) and select the set of potential communication

Elanlib is a higher level layer that frees the programmer from the revision-dependent details of the Elan, and extends Elan3lib with point-to-point, tagged message passing primitives (called Tagged Message Ports or Tports) and support for collective communication. Standard communication libraries as such MPI-2 [6] or Cray Shmem are implemented

on top of Elanlib.

User Applications

Figure 5. Elan3 Programming Library Hierarchy

#### 3.1 Elan3lib

The Elan3lib library supports a programming environment where groups of cooperating processes can transfer data directly, while protecting process groups from each other in hardware. The communication takes place at user level, with no data copying, bypassing the operating system. The main features of Elan3lib are: (1) event notification, (2) the memory mapping and allocation scheme and (3) remote DMA transfers.

#### 3.1.1 Event Notification

Events provide a general purpose mechanism for processes to synchronize their actions. The mechanism can be used by threads running on the Elan and processes running on the main processor. Events can be accessed both locally and remotely. Thus, processes can be synchronized across the network, and events can be used to indicate the end of a communication operation, such as a completion of a remote DMA. Events are stored in Elan memory, to guarantee the atomic execution of the synchronization primitives<sup>3</sup>.

## 3.1.2 Memory Mapping and Allocation

The MMU in the Elan can translate between virtual addresses written in the format of the main processor (for example, a 64-bit word, big Endian architecture such as the AlphaServer) and virtual addresses written in the Elan format (a 32-bit word, little Endian architecture). For a processor with a 32-bit architecture (for example an Intel Pentium), a one-to-one mapping is all that is required.

The MMU tables can be set up to map a common region of virtual memory called *memory allocator heap*. The allocator maps physical pages, of either main or Elan memory into this virtual address range on demand. Thus, using allocation functions provided by the Elan library, portions of virtual memory (1) can be allocated either from main or Elan memory, and (2) the MMUs of both main processor and Elan can be kept consistent.

#### 3.1.3 Remote DMA

The Elan supports remote DMA (Direct Memory Access) transfers across the network, without any copying, buffering or operating system intervention. The process that initiates the DMA fills out a DMA descriptor, which is typically allocated on the Elan memory for efficiency reasons. The DMA descriptor contains the VPIDs of both source and destination, the amount of data, the source and destination addresses, two event locations (one for the source and the other for the destination process) and other information used to enhance fault tolerance.

## 3.2 Elanlib and Tports

Elanlib is a machine independent library that integrates the main features of Elan3lib with the Tports. Tports provide basic mechanisms for point-to-point message passing. Senders can label each message with a tag, the sender identity and the size of the message. This is known as the *envelope*. Receivers can receive their messages selectively, filtering them according to the identity of the sender and/or a tag on the envelope. The Tport layer handles communication via shared memory for processes on the same node. It is worth noting that the Tports programming interface is very similar to MPI.

Elanlib provides support for collective communication operations (those that involve a group of processes). The most important collective communication primitives implemented in Elanlib are: (1) the barrier synchronization and (2) the broadcast.

# 4 Barrier Synchronization and Broadcast

## 4.1 Barrier Synchronization

A synchronization barrier is a logical point in the control flow of a parallel program at which all processes in a group must arrive before any of the processes in the group are allowed to proceed. Typically, a barrier synchronization involves a logical reduce operation followed by a broadcast.

QsNET implements two different synchronization mechanisms in Elanlib, a mixed software and hardware barrier called elan\_gsync() and a purely hardware one called elan\_hgsync().

The algorithm implemented with elan\_gsync() uses a balanced tree to send the 'ready' signal to the process with VPID 0. Each process in the tree waits for 'ready' signals from its children, and when it receives all of them sends its own signal up to the parent process. This phase of the barrier is illustrated in Figure 6. When the root process receives all its 'ready' signals it performs a hardware broadcast which either sets an event (which all processes are waiting for) or writes a single word in a given memory location (which all processes are polling). If the destination nodes

<sup>&</sup>lt;sup>3</sup>The current PCI bus implementations cannot guarantee atomic execution, so it is not possible to store events in main memory.

are not adjacent the same tree structure is used to distribute the data using point-to-point messages.

**Figure 6.** First phase of elan\_gsync() for 16 processes. Each process (1) waits for the 'ready' packet from its children and, then (2) sends its own 'ready' signal to its parent

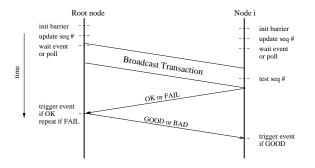

When the barrier is performed with elan\_hgysnc() or elan hqysncEvent() (Figure 7), all processes in the group set a barrier sequence number in a system memory location and wait for a 'ready' signal (busy polling on a memory location with elan\_hgysnc() or an event mechanism with elan\_hgysncEvent()). The process with VPID 0 (the root node) uses an Elan thread to send a special test-and-set broadcast packet. This packet spans all the processes and checks if the barrier sequence value in each process matches with its own sequence number (it does if the corresponding process reached the barrier). All the replies are then combined by the Elites on the way back to the root node which receives a single ACK token. If all the nodes are ready an EOP token is sent to the group to set an event or write a word to wake up the processes waiting in the barrier. It has to be noted that this mechanism is completely integrated into the network flow control (Section 2.2.1). This gives the best figures as long as the processes enter the barrier fairly close together, otherwise it backs off exponentially (to stop flooding the network with broadcasts).

**Figure 7.** elan\_hgsync() Barrier Implementation

#### 4.2 Broadcast

The main communication primitive of the QsNET is the remote DMA. A DMA operation transfers data between local and remote address spaces (including Elan memory). In addition to providing point-to-point communication, DMAs can also be used to perform group-wide operations such as broadcast and flood DMAs (a flood is similar to a broadcast but the operation completes as soon as any of the destinations accepts the DMA). A group of destination processes is defined by specifying a virtual group identifier. The effect of a write broadcast DMA is to copy the data from the source to the destination buffers of all the processes in the group. The implementation of the broadcast DMAs relies on all receiving processes having the destination buffer at the same virtual address, to obtain good performance.

QsNET provides broadcast hardware support that should send a broadcast message in the same time required to send a point-to-point message. The network can be considered as a tree of Elite switches that connect an array of Elan network interface cards. Broadcasts are propagated into the network by sending a packet to the top of the tree and then forwarding the packet to more than one switch output as the packet is sent down the tree. Deadlocks might occur on the way down when multiple broadcasts are sent simultaneously. This situation is avoided by sending broadcast packets always to a fixed top tree switch, thus serializing all broadcasts (Section 2.3). All the Elans connected to the network are capable of receiving the broadcast packet, but the hardware mechanism can only be used with a contiguous subset of Elans.

Two different broadcast implementations are provided by the Elanlib library: elan bcast() and elan\_hbcast(). Both must be called by all the processes in the group involved in the broadcast operation to guarantee that the receivers have allocated the buffers by the time the transaction is performed by the sender process. As a result, the broadcast is composed of two transactions: first, a barrier synchronization and, second, the broadcast itself. In both implementations, two types of memory resources can be used. On the one hand a global destination buffer, which has the same virtual address in all the processes (Elanlib provides special memory allocation functions to do that), allows DMA transactions directly from one source to multiple destinations. On the other hand, if this memory allocation is not used, system buffers are utilized as intermediate copy space (this approach implies one copy at the source, and another copy at the destination).

The elan\_bcast() implementation uses a software-based synchronization for the first phase similar to that utilized by the first phase of elan\_gsync() (Section 4.1). The second phase is triggered by an event set in the source node and is done using the hardware broadcast mechanism (if all the destination Elans are contiguous) or by means of a software-based broadcast (if the destination Elans are not). This transaction distributes the data and wakes up the

processes waiting in the barrier performed during the first phase. This implementation provides better performance than a call to elan\_gsync() (which involves a software-based synchronization and a broadcast) and a later broadcast to send the data.

The elan\_hbcast() primitive calls elan\_bcast() if the hardware broadcast mechanism is not available, for example when the nodes are not contiguous. If this mechanism is available, it performs a barrier to synchronize all the nodes using elan\_hgsync() (Section 4.1) and a hardware broadcast to distribute the data.

The Elan hardware broadcast can only write to the memory space of a single process per node since there is only a single context specified by the virtual process identifier. Hence, with multiple processes per node, the only way to use the hardware broadcast facility is to broadcast into an area of shared memory and then get the processes to copy from there. This has been optimized by using a FIFO like scheme that tries to overlap the broadcast with the copies.

## 5 Experimental Framework

The main features of the QsNET were tested on a 64-node cluster of Compaq AlphaServer ES40s, running Tru64 Unix. Each AlphaServer node is equipped with 4 Alpha 667MHz 21264 processors, 8GB of SDRAM and two 64-bit, 33MHz PCI I/O buses. The Elan3 QM-400 card is attached to one of these and links the SMP to a quaternary fat tree of dimension three, like the one shown in Figure 2 c).

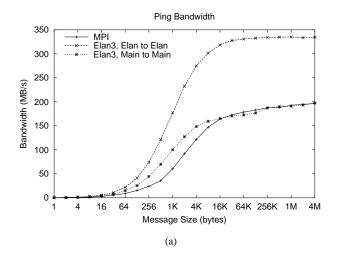

## 5.1 Unidirectional Ping

We analyze the latency and bandwidth of the network by sending messages of increasing sizes. In order to identify different bottlenecks, the communication buffers are placed either in main or in Elan memory. The alternatives include main memory to main memory and Elan memory to Elan memory. These buffers are placed in the desired type of memory using the allocation mechanisms provided by Elan3lib, as described in Section 3.1.

The latency is measured as the elapsed time between the posting of the remote DMA request and the notification of the successful completion at the destination. The unidirectional ping tests for MPI are implemented using matching pairs of blocking sends and receives. These tests provide a performance reference to consistently analyze the results on collective communication.

## **5.2** Collective Communication

The barrier synchronization and broadcast primitives provided by the QsNET system software have been tested using configurations ranging from 4 to 64 nodes. Results

have been obtained by averaging the results over 10000 consecutive tests. Average latency results and latency distribution are reported for the barrier synchronization tests. For the broadcast tests bandwidth and latency are reported.

In addition, tests with background traffic have been performed to analyze the behavior of the collective communications under network contention. This background traffic is generated by 128 processes running in 64 nodes (one sender and one receiver per node), with all nodes injecting messages into the network at maximum load. The goal of these tests is to identify the performance degradation experienced by the collective communication in the presence of congestion. Two different traffic patterns were used to generate background traffic:

- Complement. The node with binary coordinates  $a_{n-1}, a_{n-2}, \ldots, a_1, a_0$  communicates with the node  $\overline{a_{n-1}, a_{n-2}, \ldots, a_1, a_0}$ . This pattern uses all the network links at the same time.

- Uniform. Each node selects randomly its destination for every single transaction.

To guarantee that the performance degradation of the collective communication is only due to the network contention and not to scheduling issues, the background traffic generation and the collective communication benchmark were run in distinct processors.

## 6 Experimental Results

## 6.1 Unidirectional Ping

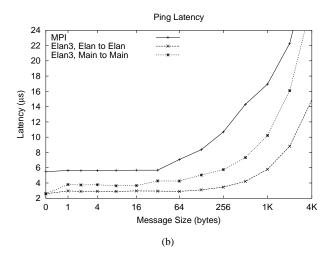

Figure 8 a) shows the performance of the unidirectional ping. The peak bandwidth of 335 MB/s is reached when both source and destination buffers are placed in the Elan memory. The maximum amount of data payload that can be sent by the current Elan implementation in a packet is 320 bytes, partitioned in five low-level write-block transactions of 64 bytes. For this packet format, the overhead is 58 bytes, for the message header, CRCs, routing info, etc. This implies that the delivered peak bandwidth is approximately 396 MB/s, or 99% of the nominal bandwidth (400 MB/s). The asymptotic bandwidth for main memory to main memory communication is only 200MB/s for both Elanlib and MPI. These results also show that the PCI interface running at 33MHz is the bottleneck for this type of communication.

Figure 8 b) shows the latency in the range [0...4KB]. With Elan3lib the basic latency for 0-byte messages is only 2.2  $\mu$ s and is almost constant at 2.4  $\mu$ s for messages up to 64 bytes, because these messages can be packed as a single write-block transaction. We note an increase in the latency at MPI level, compared to the latency at the Elan3lib level, from approximately 2  $\mu$ s to 5.5  $\mu$ s. While at Elan3lib level the latency is mostly hardware, MPI needs to run a thread in the Elan microprocessor in order to match the message

tags: this introduces the extra overhead responsible for the higher latency.

Figure 8. Unidirectional Ping

#### **6.2** Collective Communications

# **6.2.1** Barrier Synchronization

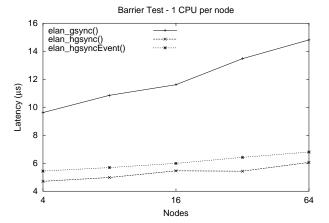

Figure 9 shows the average time required to perform a barrier synchronization in an empty network. Results for the three Elanlib primitives (Section 4.1) are shown versus the number of nodes. We can see that the hardware-based implementations of the barrier (elan\_hgsync() and elan\_hgsyncEvent()) provide the best results when compared to the software-based implementation (elan\_gsync()), both in absolute performance and in scalability. The latency of the software-based implementation grows as the logarithm of the number of nodes (approximately  $2.5\mu s$  each time the number of nodes is quadrupled). In this case the average latency to syn-

Figure 9. Barrier Synchronization

chronize 64 nodes is  $14.8\mu s$ . On the other hand, the elan\_hgsync() barrier provides an average latency of  $5\mu s$  below 16 nodes and  $5.5\mu s$  and  $6\mu s$  for 32 and 64 nodes, respectively. The elan\_hgsyncEvent() synchronization gives latencies on average  $0.7\mu s$  above those obtained with elan\_hgsync(). This is due to the additional delay associated with the event notification. In both thread based barriers, the latency increase above 16 nodes is probably due to scheduling issues on the OS (Tru64 Unix).

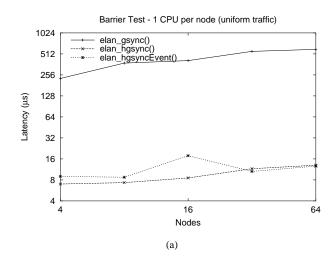

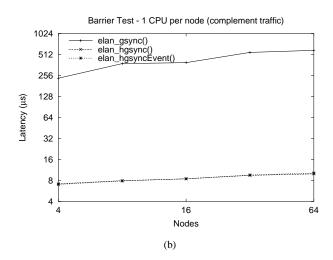

The behavior of the barrier synchronization has been analyzed by performing tests with uniform and complement background traffic. The results depicted in Figure 10 show that the performance of the various barrier implementations is affected by the network traffic with higher degradation when uniform background traffic, which produces higher network contention, is used (note that the latency scale is logarithmic in this figure). In fact, with complement traffic there is always one virtual channel available in each link. The software barrier is significantly affected by the background traffic, the slowdown is 40 in the worst case of uniform traffic and 64 nodes. On the other hand, there is little impact on the hardware barriers, whose latency is only doubled. The scalability is also affected by the background traffic, with no significant differences with uniform traffic for the three implementations tested. In this case, the latency increase with the number of nodes is tripled; for example, the elan\_gsync() latency increases 54% (when the number of nodes varies from 4 to 64) with no background traffic and 160% with uniform traffic while the elan hgsync() latency increases 29% and 86%, respectively. With complement traffic the performance of the software-based barrier is similar (an increase of 150% in latency) while the hardware-based implementations provide a better scalability (an increase of 40%). The softwarebased barrier latency scalability is shown to be more sensitive to complement background traffic than the hardwarebased barriers.

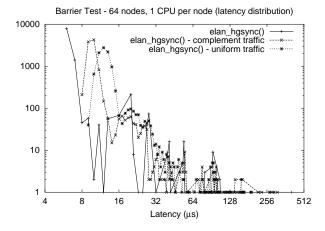

Figure 11 shows the latency distribution of

elan\_hgsync() in a 64-node configuration for experiments with 10000 consecutive tests. Only 2% of the operations take more than  $20\mu s$  and 94% less than  $9\mu s$  when there is no background traffic. In the most congested case, with uniform background traffic, the average latency for 64 nodes is  $14.8\mu s$ , with more than 93% of the barriers taking less than  $20\mu s$ . Similar results were obtained with elan\_hgsyncEvent().

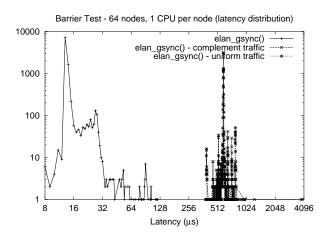

The latency distribution for the software-based implementation of the barrier synchronization is shown in Figure 12. Only 1% of the barriers take more than  $30\mu s$  in an empty network. In the presence of network contention, elan\_gsync() suffers a significant degradation in performance. In the worst case (uniform background traffic) an average latency of  $595\mu s$  is obtained and 93% of the synchronizations complete with latencies below  $605\mu s$ .

Figure 10. elan\_hgsync() Latency with Contention

**Figure 11.** elan\_hgsync() Latency with Contention

**Figure 12.** elan\_gsync() Latency with Contention

#### 6.2.2 Broadcast

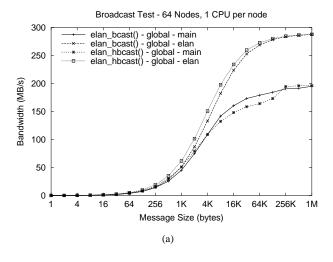

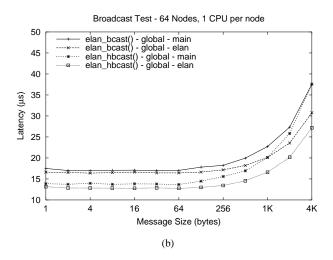

Figure 13 shows the results obtained with broadcast over 64 nodes using both algorithms supported by Elanlib (Section 4.2) with buffers globally allocated in main and Elan memory, that is, with the same virtual address in all processes. The best performance is obtained, as expected, with Elan memory. In this case the measured bandwidth for 1MB messages is 288MB/s for both elan\_bcast() and elan\_hbcast(). The elan\_hbcast() primitive provides lower latencies (a difference of  $3.5\mu s$ ) because it uses the hardware-based synchronization rather than the software-based one. For this reason the bandwidth for shorter messages is slightly higher with elan\_hbcast(). For messages up to 256 bytes the latency is constant and approximately equal to  $13\mu s$  for elan\_hbcast() and  $16.5\mu s$  for elan\_bcast(). This is due to the fact that messages shorter than 320 bytes are sent using a single packet [12].

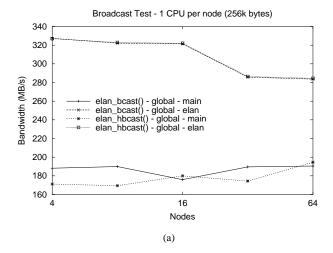

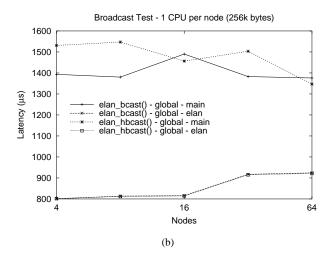

Bandwidth and latency versus the number of nodes for 256KB messages are depicted in Figure 14. Both performance metrics are insensitive to the number of nodes when

Figure 13. Broadcast

Figure 14. Broadcast Scalability

the buffers are allocated in main memory, because the PCI bus is the bottleneck in this case. On the other hand, when Elan memory is used, a performance degradation occurs when the number of nodes increases above 16 (8% decrease in bandwidth and 12% increase in latency). A similar, albeit lower, effect is experienced when the number of nodes is increased above 4 (1% differences in bandwidth and latency).

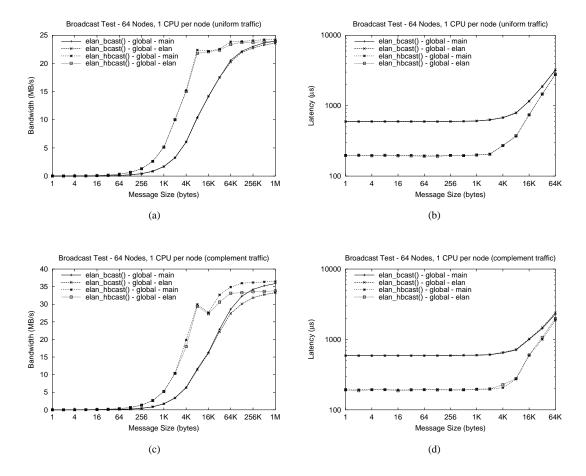

In the presence of network contention (Figure 15) the broadcast performance decreases significantly. The maximum bandwidth is obtained by using main memory. This is caused by the job running in the background which allocates its communication buffers in Elan memory. This configuration gives 36MB/s with complement background traffic and 24MB/s with uniform background traffic using 1MB messages. Although both broadcast implementations provide approximately the same maximum bandwidth (with 1MB messages), the elan\_hbcast() primitive obtains better performance for smaller messages due to the hardware synchronization mechanism (Figures 15 (b) and (d)), which is

less sensitive to additional network traffic (Section 6.2.1).

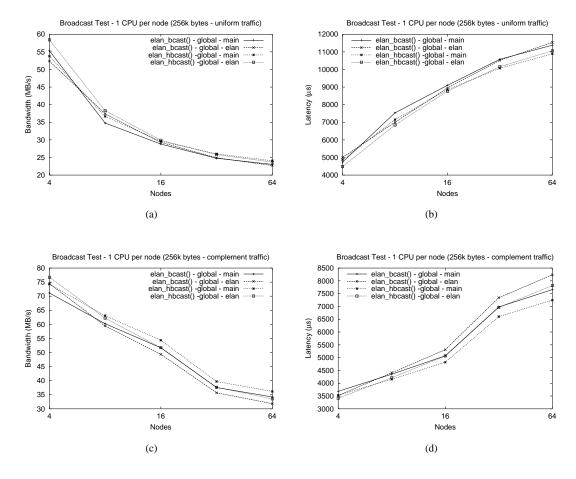

In terms of scalability (Figure 16) the four alternatives suffer from the same performance degradation as the number of nodes increases. This effect slows down as we increase in the number of nodes, suggesting that no additional significant performance decrease should be experienced by networks larger than 64 nodes.

# 7 Conclusion

In this paper, we presented an in-depth description of the Quadrics interconnection network (QsNET) with special emphasis on the support for collective communication and its integration with the system software. We focused on two basic communication patterns: barrier synchronization and broadcast. An experimental evaluation of hardwarebased and software-based implementations of these services has been performed on a 64-node AlphaServer cluster.

Figure 15. Broadcast with Contention

Our experiments show that the time to complete a hardware-based barrier synchronization on the whole set of nodes is as low as  $6\mu s$ , with very good scalability for the network configurations tested. Good latency and scalability are also achieved with the software-based synchronization, which completes in  $15\mu s$ .

Another important contribution of this paper is the analysis of the collectives in the presence of network contention. In this case, the average latency for the hardware barrier is  $13\mu$ s, with 93% of the synchronizations taking less than  $20\mu$ s. On the other hand, the software-based implementation is shown to suffer a significant performance degradation. From a practical point of view the hardware-based barrier can be considered insensitive to network contention.

With the broadcast, similar results have been obtained for the hardware-based and the software-based implementations in the absence of additional network traffic. These results show that without contention the two algorithms can be used interchangeably. The broadcast latency for messages up to 256 bytes is  $13\mu s$  and the bandwidth is 288MB/s. Contention tests, done in the presence of high network load, show that the broadcast maintains reasonably good performance (i.e. less than  $200\mu s$  to deliver mes-

sages up to 2KB). In this case the hardware-based broadcast outperforms the software-based broadcast thanks to its hardware-based synchronization mechanism. Overall, our analysis shows the potential of the interconnect to efficiently support large-scale collective communication, even in the presence of high network contention. As future work, we plan to address the problem of the serialization of the hardware broadcasts on the root node and to study how collective communication can be further integrated with the network processor.

# Acknowledgements

The authors would like to thank the Quadrics team, David Addison, Jon Beecroft, Robin Crook, Moray McLaren, David Hewson, Duncan Roweth and John Taylor, for their invaluable support.

## References

[1] G. Bell. Ultracomputer: a Teraflop Before its Time. *Communications of the ACM*, 35(8):27–47, 1992.

Figure 16. Broadcast Scalability with Contention

- [2] Nanette J. Boden, Danny Cohen, Robert E. Felderman, Alan E. Kulawick, Charles L. Seitz, Jakov N. Seizovic, and Wen-King Su. Myrinet: A Gigabit-per-Second Local Area Network. *IEEE Micro*, 15(1):29–36, January 1995.

- [3] Darius Buntinas, Dhabaleswar Panda, and P. Sadayappan. Performance Benefits of NIC-Based Barrier on Myrinet/GM. In Workshop on Communication Architecture for Clusters (CAC '01), San Francisco, CA, April 2001.

- [4] William J. Dally and Charles L. Seitz. Deadlock-Free Message Routing in Multiprocessor Interconnection Networks. *IEEE Transactions on Computers*, C-36(5):547–553, May 1987.

- [5] José Duato, Sudhakar Yalamanchili, and Lionel Ni. Interconnection Networks: an Engineering Approach. IEEE Computer Society Press, 1997.

- [6] Al Geist, William Gropp, Steve Huss-Lederman, Andrew Lumsdaine, Ewing Lusk, William Saphir, Tony Skjellum, and Marc Snir. MPI-2: Extending the Message Passing Interface. In Second International Euro-Par Conference, Volume I, number 1123 in LNCS, pages 128–135, Lyon, France, August 1996.

- [7] Charles E. Leiserson. Fat-Trees: Universal Networks for Hardware Efficient Supercomputing. *IEEE Transactions on Computers*, C-34(10):892–901, October 1985.

- [8] Fabrizio Petrini and Marco Vanneschi. k-ary n-trees: High Performance Networks for Massively Parallel Architectures. In Proceedings of the 11th International Parallel Processing Symposium, IPPS'97, pages 87–93, Geneva, Switzerland, April 1997.

- [9] Fabrizio Petrini and Marco Vanneschi. Performance Analysis of Wormhole Routed k-ary n-trees. *International Journal on Founda*tions of Computer Science, 9(2):157–177, June 1998.

- [10] G. F. Pfister and V. A. Norton. Hot-spot Contention and Combining in Multistage Interconnection Networks. *IEEE Transactions on Computers*, C-34(10):943–948, October 1985.

- [11] Quadrics Supercomputers World Ltd. Elan Programming Manual, January 1999.

- [12] Quadrics Supercomputers World Ltd. Elan Reference Manual, January 1999.

- [13] Quadrics Supercomputers World Ltd. Elite Reference Manual, November 1999.

- [14] Rajeev Sivaram, Dhabaleswar Panda, and Craig Stunkel. Efficient Broadcast and Multicast on Multistage Interconnection Networks using Multiport Encoding. In *Proceedings of the 8th IEEE Symposium* on Parallel and Distributed Processing, New Orleans, LA, October 1996.

- [15] Rajeev Sivaram, Dhabaleswar Panda, and Craig Stunkel. Multicasting in Irregular Networks with Cut-Through Switches using Tree-Based Multidestination Worms. In *Parallel Computing, Routing, and Communication Workshop, PCRCW'97*, Atlanta, GA, June 1997.

- [16] Thorsten von Eicken, David E. Culler, Seth Copen Goldstein, and Klaus Erik Schauser. Active Messages: a Mechanism for Integrated Communication and Computation. In *Proceedings of the 19th International Symposium on Computer Architecture*, Gold Coast, Australia, May 1992.